# Akraino Release 7 Review of IEC Type 5

LEO li@socnoc.ai

2023.1.18

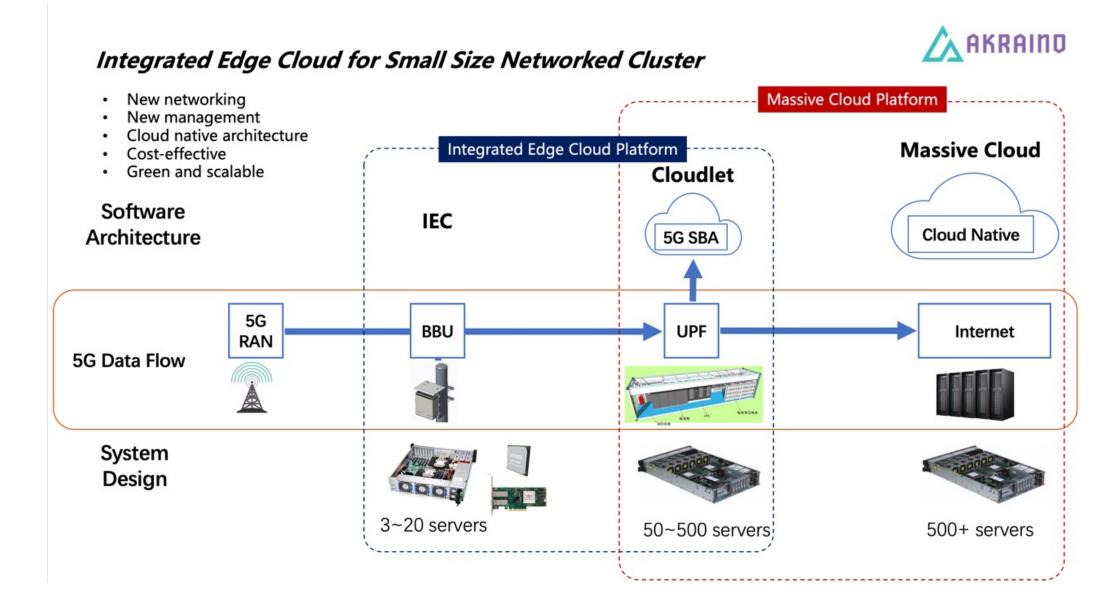

#### **Integrated Edge Cloud Overall Introduction**

#### **Integrated Edge Cloud Road Map**

Introduce the VPX cluster design for IEC

Backplane networking Consolidate ethernet switch Release 8

Release 7

More general server design for *edge*

cluster

OCP?

UCle?

Introduce the PCIe Network PCIe networking Run TCP/IP over PCIe

Release 6

#### [Release7] System Architecture

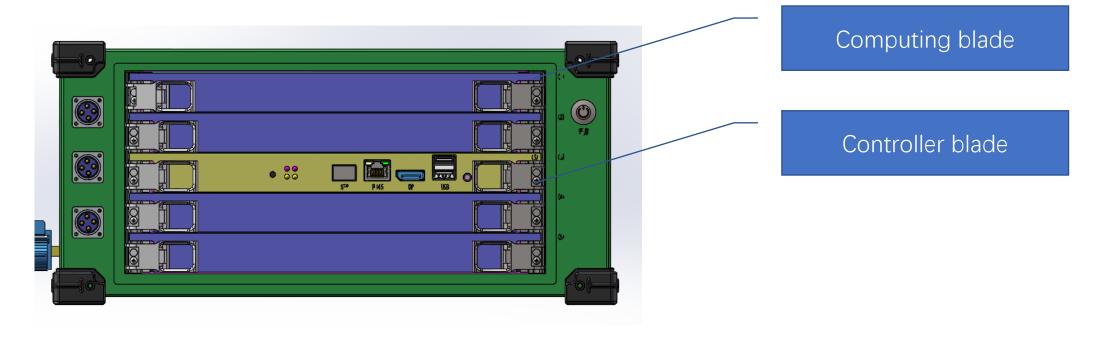

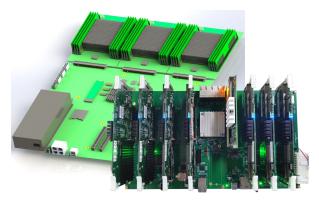

The prototype consists of the main controller blade, compute blade, switching backplane, heat dissipation system, power supply, and chassis.

- Sturdy formfactor for outdoor scenarios, without datacenter environment

- Resilient design with two controller blade for high-availability

- Extendable with multiple computing blades, up to 15 nodes (14 with two controller blades)

- K8s ready (ubuntu/centos)

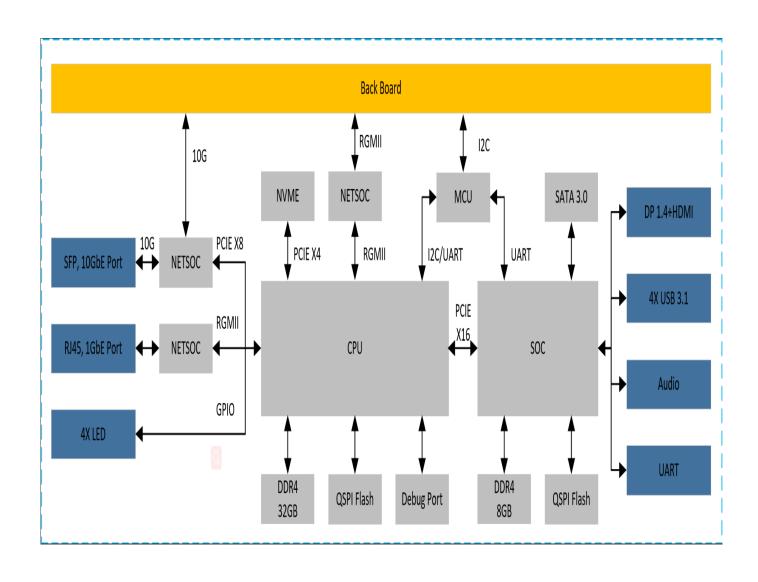

#### [Release7] Main Control Blade Architecture

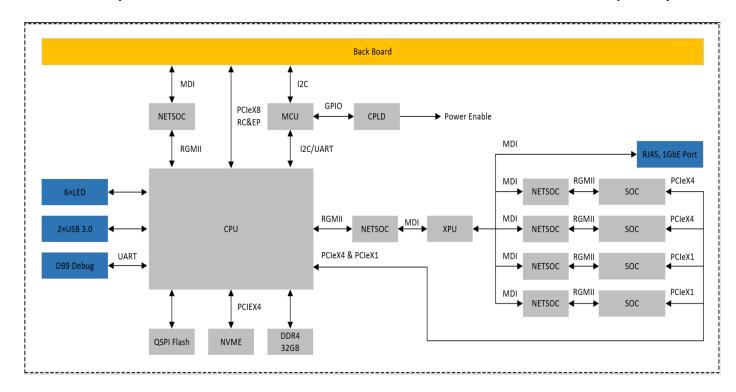

#### [Release7] Compute Blade Architecture

- 1. To provide back PCle Gen 3 by 8 signal, can be configured to RC and EP;

- 2. To provide back 1 gbe MDI network signal;

- 3. To provide back IPMI management based on 12 c interface; To provide panel 1 gbe network, USES the RJ45 interface;

- 4. To provide panel debug serial port, using the DB9 interface;

- 5. Provide panel with two USB 3.0 interface, using the Type A interface; Provide panel with six software programmable control indicator light;

- 6. CPU by PCle Gen3X4 mount NVME hard disk, hard disk capacity of not less than 256 gb;

- 7. Using DDR4 as a memory, not less than 32 gb capacity, interface physical rate not less than 3200 MTPS;

- 8. Through the network exchange chip 4 soc and XPU connection module, access rate to 1 GBPS;

- 9. Each SOC module USES LPDDR4X memory, not less than 8 gb capacity, rate of not less than 4266 MTPS;

- 10. CPU through two PCle Gen3X4 and 2 PCle Gen3X1 four SOC and connectivity;

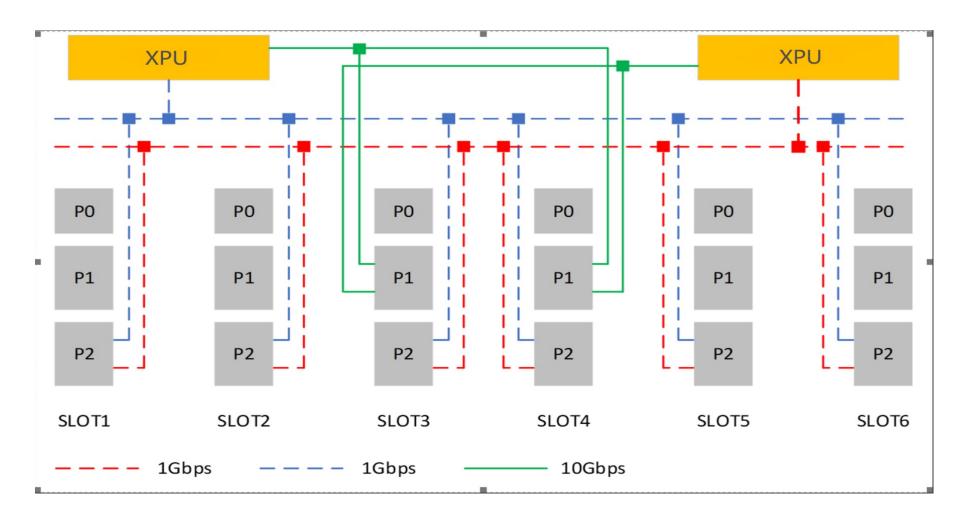

#### [Release7] Switching Backplane Architecture

Using XPU in exchange for chips, two pieces of XPU are redundant;

Each XPU can provide up to eight 1 gbe port, each slot P2 side provide 2 road 1 gbe interface to be redundant XPU;

Each XPU can provide up to two 10 gbe port, the P1 end of the slot number 3 and 4 provide 2 road 10 gbe interface to the XPU are redundant

Back to the slot provides IPMI management interface based on 12 c, located in each slot P0 end;

Back to the slot provides auxiliary power AUX + 5 v and + 12 v power supply, is located in each slot P0 end;

The backplane provides the engine fan power supply and control.

### [Release 6 + 7] Continuous Evolving of Networking on Edge **System**

**R6** server

**R7** cluster

**R8** UCle?

## Thank You!